[이코리아] 네덜란드의 글로벌 반도체 장비 기업인 ASML의 차세대 극자외선(EUV) 노광 장비가 미국 반도체 기업 인텔로 처음 출하됐다. 2나노미터(nm, 10억분의 1m) 첨단 반도체 양산을 계획 중인 삼성전자는 인텔보다 뒤늦게 이 장비를 받게 되면서 거센 추격을 받게 될 것으로 보인다.

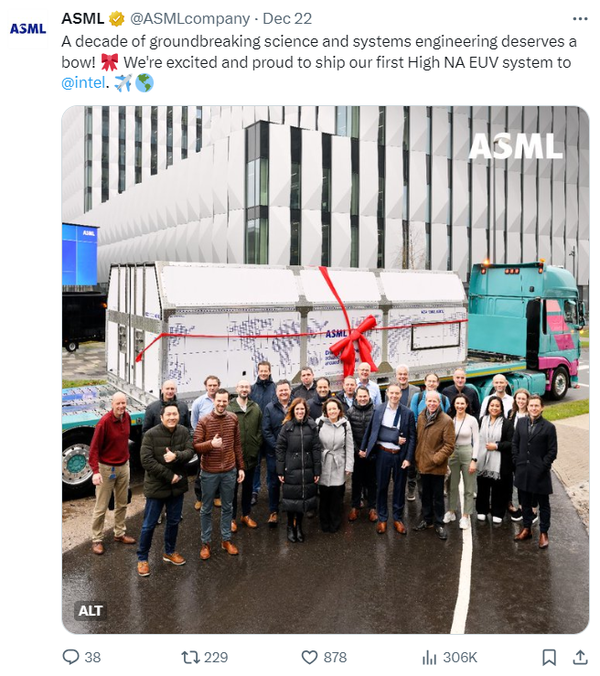

로이터 통신은 21일(현지시간) ASML이 이날 새로운 ‘하이 NA EUV’(High-NA EUV) 리소그래피 시스템의 첫 번째 제품을 인텔사로 배송했다고 보도했다.

트윈스캔(Twinscan) EXE:5000 EUV 스캐너는 AMSL 최초의 파일럿 하이-NA 스캐너로, 최근 네덜란드를 국빈 방문해 직접 ASML 본사를 찾은 윤석열 대통령도 언급했던 초미세 공정용 차세대 장비다.

앞서 인텔은 2018년에 처음 이 장비를 주문했다. 또한 2022년에 ASML의 상용 등급 트윈스캔 EXE:5200 장비도 최초로 주문했다.

지난해 ASML은 2027년부터 2028년까지 연간 20개의 하이 NA EUV 장비를 생산할 수 있을 것이라고 발표했다.

인텔 외에 이 장비를 주문한 반도체 업체들로는 삼성전자를 비롯해, SK하이닉스, TSMC, 마이크론 등이라고 외신은 전했다.

이번에 ASML이 인텔에 납품하는 하이 NA EUV 장비는 미국 오레곤 주의 힐스보로 인근 인텔 D1X 공장으로 배송된다.

IT전문지 아난드테크는 이날 ASML의 차세대 EUV 노광장비에 대해 “0.55 NA 렌즈가 장착된 하이 NA EUV 장비는 8nm 해상도가 가능하며, 이는 13nm 해상도의 현재 EUV 도구와 비교했을 때 상당히 개선됐다”고 평가했다.

이어 “이러한 차세대 하이 NA EUV 스캐너는 팹이 EUV 이중 패터닝을 사용하지 않도록 해 잠재적으로 수율을 향상시키고 비용을 절감할 수 있을 것”이라면서 “업계에서 2025년부터 2026년까지 채택할 예정인 3나노 이상의 공정 기술을 사용한 칩 생산에 중요할 것으로 예상된다”고 밝혔다.

하이 NA EUV 장비가 기존의 EUV 장비에 비해 크기가 더 커진 것 외에 더 높은 해상도와 다른 레티클 크기를 지원하기 때문에 업체들이 새로운 포토레지스트, 계측, 펠리클 재료, 마스크 및 검사 도구가 필요할 것으로 보인다고 아난드테크 측은 지적했다. 즉, 하이 NA 장비를 사용하려면 인프라에 상당한 투자가 필요하다는 의미다.

ASML의 하이 NA EUV 장비를 운송하기 위해 13개의 트럭 크기의 컨테이너와 250개의 상자가 필요하다. 일단 조립되면, 그 기계는 3층 높이에 달한다. 이에 ASML 측이 기계 배송에 앞서 인텔이 층고가 더 높고 새로운 팹 확장을 요구한 것으로 알려졌다. 각각의 하이 NA EUV 장비는 대략 3억~4억 달러(약 3885억~5180억 원)사이의 높은 가격대일 것으로 업계는 추정하고 있다.

인텔은 이번에 납품받는 장비를 비롯해 6대를 선제적으로 확보한 것으로 알려졌다. 삼성전자는 2025년 경 확보될 전망이다.

인텔은 2025년에 대량 제조(HVM)를 위한 상용 등급 트윈스캔 EXE:5200 장비를 배포하기 전에 하이 NA EUV를 사용할 것으로 알려졌다.

인텔은 2024년 2나노에 진입한 뒤 2025년 1.8나노를 선보이겠다는 계획을 천명한 바 있다. 지난 9월 19일(현지시간) 미국 캘리포니아 컨벤션센터에서 열린 ‘이노베이션 2023’에서는 18A 시제품 웨이퍼를 깜짝 선보이기도 했다. 18A는 1.8 나노급으로, 인텔은 내년 1분기부터 양산 준비에 돌입해 2025년 출시한다는 계획이다.

업계에서는 인텔이 2024년에 18A 노드에 대한 개발 작업을 시작한 다음 2025년에서 2026년 사이에 포스트 18A 노드에 하이 NA 장비를 사용할 것으로 관측하고 있다. 앞서 삼성전자와 TSMC는 2025년 2나노 공정 양산에 돌입할 예정이라 밝혔다.

업계 한 관계자는 “인텔이 경쟁사들보다 더 일찍 하이 NA 장비를 구입함으로써 2나노 등 첨단반도체 제조를 보장할 수 있을 뿐만 아니라 하이 NA 제조와 관련해 업계 표준을 설정할 수 있는 기회를 갖게 됐다”고 말했다.

다만, 인텔이 파운드리 후발 기업인 것을 감안, 차세대 장비를 바로 들여도 기술력이 앞선 삼성전자를 바로 추월하기에는 무리가 있을 것이라는 분석도 나온다.

3나노 양산을 앞두고 있는 파운드리 투톱인 삼성전자와 TSMC와는 달리 인텔은 현재 7나노 칩을 양산하고 있기 때문이다. 게다가 인텔의 7나노 양산도 안정적이지 못하다는 게 반도체 업계의 중론이다.

김양팽 산업연구원 반도체 전문 연구원은 27일 <이코리아>와 한 통화에서 “차세대 장비를 이용하는 인텔의 2나노 생산 가능성이 다른 기업보다 많이 높아졌다고 말할 수 있다. 반도체/디스플레이를 장치산업이라고 부르는 이유가 이런 것 때문”이라고 말했다.

김 연구원은 이어 “하지만 2나노를 차세대 EUV 장비만으로 만들 수 있는 것은 아니다. 삼성전자나 TSMC는 이러한 장비 없이도 2나노가 가능하도록 단계적으로 제조공정 기술을 쌓고 있다. 이러한 단계적 기술을 바탕으로 한 수율은 아무래도 안정되게 마련”이라고 설명했다.

그러면서 “인텔이 2나노를 생산한다고 해도 5000억 원대의 장비를 이용한 만큼 이미 제조원가에서 차이가 난다. 2나노 생산과 2나노의 수율 및 경제성 충족은 완전히 다른 이야기”라고 지적했다.

김 연구원은 “새로운 반도체 공정은 제조공장에서 최소 6개월에서 1년 정도 장비 안정화 작업을 거쳐야 한다. 인텔의 2나노 공정 출시는 빨라야 내년 말로 예상된다”면서 “엔비디아나 퀄컴이 이제 3나노 제품을 하나 둘씩 시장에 내는 단계다. 시장은 3나노도 무르익지 않았는데, 설사 인텔이 내년에 2나노 공정을 출시한다고 해도 얼마나 많은 기업이 필요로 할런지는 고민해 볼 문제”라고 말했다.